ЭВМ и периферийные устройства - 1

для специальности 220300

Прищепа Л.С.

Кафедра КСУП

Томск-2002

№ 1

Свойства алгоритма:

• Алгоритм – это план c ограниченными свойствами.

№ 2,10

Формат команды (регистра команд) П-машины:

• КОП.В.С.

№ 3

Отличие плана и алгоритма решения в отношении наборов данных:

• Массовость.

№ 4

- в отношении указания следующего шага решения:

• Определенность.

№ 5

- выполнения очередного шага решения:

• Результативность.

№ 6

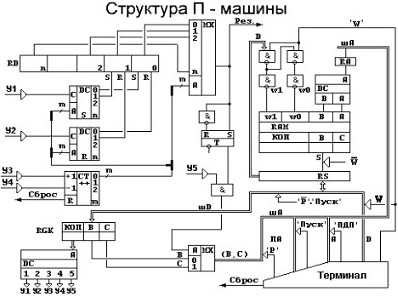

Структура П-машины. Выходы ДС (S, R) соответствуют разрядам RD:

• RDj : = DCj (S,R).

№ 7

В регистре данных RD для П-машины использован элемент памяти:

• R-S триггер.

№ 8

Организация записи и чтения разрядов регистра данных:

• DC(S); DC(R); MX(REZ); RD; CT.

№ 9

Согласование разрядности RD и счетчика СТ разрядов П-машины:

• n = 2 ** m.

№ 11

Организация чтения полей В и С регистра команд П-машины:

• Y5&MX(REZ), RD, MX(B,C), RGK, MX(REZ).

№ 12

Подключение шины (В, С) к адресной шине шА П-машины организовано:

• Сигналом “Р” пультового терминала.

№ 13

Состояние выхода элемента И, управляющего мультиплексором отсылок (В, С) для П-машины:

• RD, MX(REZ),СТ,Y5&MX(REZ).

№ 14

Шина А (терминала) к шине шА для П-машины подключена:

• Сигналом “ПДП” пультового терминала.

№ 15

Шина D (терминал) к шине шD для П-машины:

• Сигналом “W” пультового терминала.

№ 16

Связь порта RS ввода-вывода ОЗУ с шD и RAM для П-машины:

• RS:=RAM&W; шD:=RS&P &ПУСК.

№ 17

Передача данных из RAM в регистр команд RGK для П-машины:

• RGK:= шD; шD:=RS&P &ПУСК; RS:=W &RAM.

№ 18

Запись в RAM:

• A, D, W.

№ 19

Последовательность активизации структурных элементов П-машины в режиме записи адреса сообщения в ОЗУ:

• терминал, шА, RA, DC, RAM.

№ 20

- при передаче данных к ОЗУ:

• терминал, шинаD, шD, RS, RAM.

№ 21

Функции порта ввода-вывода ОЗУ П-машины:

• Организует связь шD с ОЗУ.

№ 22

Достаточны и необходимы при записи команд в ОЗУ П-машины данные:

• A, D, W.

№ 23

- для чтения из памяти:

• A, W.

№ 24

ОЗУ к процессору БУ ЭВМ в режиме “чтения”:

• подключено к шине данных шD процессора через порт RS ввода-вывода, управляемый сигналами Y1 или Y4 или Y6.

№ 25

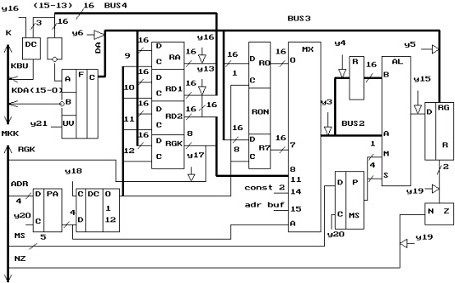

Для ввода-вывода данных в БУ ЭВМ использован регистр РАЛУ:

• RG.

№ 26

Для БУ ЭВМ:

• Сигнал Y5 управляет портом RG ввода-вывода РАЛУ: Y5 = 1 – чтение данных, а Y5 = 0 – запись данных.

№ 27

Признаки ЗНАК, НУЛЬ результата в РАЛУ определены по содержимому регистра АКК.

№ 28

Запись на дополнительный регистр R арифметико-логического устройства БУ ЭВМ организует управляющий сигнал:

• Y1.

№ 29

- передачу адреса данных для ОЗУ в БУ ЭВМ:

• Y2.

№ 30

- передачу адреса очередной команды в БУ ЭВМ:

• Y3.

№ 31

- передачу данных для ОЗУ из РАЛУ в БУ ЭВМ:

• Y5.

№ 32

- передачу данных из ОЗУ в РАЛУ:

• Y5 и (Y1 или Y4).

№ 33

- ввод данных в RGK для БУ ЭВМ:

• Y6.

№ 34

- модифицируют счетчик команд СТАК в БУ ЭВМ:

• Y7 или Y8.

№ 35

Формат команды БУ ЭВМ. “Длина” команды группы АО в зависимости от бита PZ:

• РZ=1 – удлиняется.

№ 36

Команда посылочной группы при назначении бита PZ (0/1) для БУ ЭВМ:

• PZ=0 – прием данных для РАЛУ, PZ=1 – выдача данных из РАЛУ.

№ 37

Подключение внешнего устройства (ВУ) к процессору БУ ЭВМ.

• шА:= RGK(А); Y20) РА:=шА; Y22) RG:=F(C);

Y21, Y24) PS ↔ F, YB:= (0,1); Y23) F(А):= RG.

№ 38

Подключение процессора БУ ЭВМ к ВУ организует элемент системы:

• F(YB), шА.

№ 39

Как единообразно процессор начинает обмен с ВУ для БУ ЭВМ:

• Y20) PA:=шA, шA:=RGK(A).

№ 40

Циклы обмена ВУ при чтении или записи данных для БУ ЭВМ:

• Отличие заключается в направлении передачи данных и моментом поступления сигнала синхронизации процесса: прием данных для ВУ, затем сигнал WW; сначала сигнал RR, затем передача данных из ВУ.

№ 41

Адрес обращения к ВУ необходимо сохранять, так как интервал приема А и интервал работы с D разделены во времени.

№ 42

Запись данных в ВУ от БУ ЭВМ:

• PA:=RGK(A); PS:=RG; сигнал WW.

№ 43

Чтение данных ВУ в БУ ЭВМ:

• PA:=RGK(A); сигнал RR; RG:=PS.

№ 44

Направление обращения к ВУ от БУ ЭВМ определено управляющим сигналом:

• Y20, YB(0,1).

№ 45

Размещение трех слов команды в процессоре:

• RA, RD1, RGK.

№ 46

Выборка слов команды из ОЗУ:

• RА:=R7, Y6, DA, Y16, F(Y21), BUS4, BUS3, Y18, микропрограмма с приемником (RGK или RA или RD1).

№ 47

Записи формата команды, данных и адресов представлены в:

• Восьмеричной системе счисления.

№ 48

В формате команды источник или приемник данных определены:

• Методами адресации SS и DD.

№ 49

Методы адресации источника или приемника данных:

• в формате команды с фиксированной разрядностью используют по той причине, что в ее разрядной сетке не хватает места для данных и адреса.

№ 50

Известно:

• Восемь методов адресации.

№ 51

К системному каналу РАЛУ подключено средствами:

• KBY, KAD, F(Y21).

№ 52

Элементы РАЛУ связывают шины:

• BUS1, BUS2, BUS3, BUS4.

№ 53

В составе РАЛУ являются рабочими регистры:

• RA, RD1, RD2, RGK.

№ 54

Регистров общего назначения:

• Восемь.

№ 55

Подключены к микроканалу регистры:

• PMS, RGK, PA, NZ.

№ 56

Функция мультиплексора МХ:

• Читает R0…R7, RGK, RD1, RD2, константы и загружает шину BUS2.

№ 57

Организация шин BUS в схеме РАЛУ:

• Мультиплексируемые управляемые.

№ 58

Результат обработки данных хранится в:

• RGR.

№ 59

Дешифратор ДС (РА):

• Синхронизирует чтение данных BUS3.

№ 60

Логические цепи при организации пересылки (Ri:=Rj). Значения полей PMS, PA микрокоманд:

• RGR:= Rj, PMS = 1, PA = j; Ri:=RGR, PA=i.

№ 61

Функции рабочих регистров:

• Хранят адрес, операнды и первое слово команды.

№ 62

Входы шины BUS3:

• DA и REZ.

№ 63

Управляющие сигналы (или биты микрокоманды) для передачи данных между регистрами РАЛУ:

• Y20, Y3, Y15, Y5, Y18.

№ 64

Операнды на входы А и В арифметико-логического устройства поступают:

• через BUS2 и R.

№ 65

Включение дополнительного регистра необходимо в цепи:

• Входа В и выхода АЛУ.

№ 66

Каждая микрокоманда секции 9 образует логические цепи:

• Ri – MX – BUS2 – R; RJ – MX – BUS2 – АЛУ – RGR; RGR – BUS3 - Rj.

№ 67

- выполняет функцию:

• R:= RE; RGR:= RK*R; RK :=RGR.

№ 68

Для АОС3 загружать R7 перед исполнением последовательности секций микропрограмм необходимо, чтобы указать адрес первого слова интерпретируемого фрагмента программы пользователя.

№ 69

Общность в исполнении функций микропрограммных секции 10 и 9:

• проявляется в том, что они реализуют операции межрегистрового обмена и имеют микрооперацию Ri:=RGR.

№ 70

Различия -

• в том, что они реализуют или пересылку, или обработку или одноместных, или двухместных операций над данными.

№ 71

Операция “Сравнение” выполняется так: R:=DD, BUS2:=SS, RGR:=BUS2 – R.

№ 72

Отличия выполнения операции “Сравнение” от операции “Вычитание”:

• “Сравнение”: R:=DD, BUS2:=SS, RGR:=BUS2 - R; “Вычитание”: R:=SS, BUS2:=DD, RGR:=BUS2 - R, DD:=RGR.

№ 73

Подготовку обработки двухместных операций организуют сигналы:

• Y3, Y4.

№ 74

Вычисление признаков N и Z результата операции:

• RGR = 0, то Z = 1, N = 0.

№ 75

Вычисление RGR : = RDI + RD2 возможно.

№ 76

RD1и RD2 присвоен адрес:

• 9 и 10.

№ 77

Входные данные AЛУ и результат представлены в:

• Двоичной системе исчисления.

№ 78

Обращение процессора к каналу подтверждено системным сигналом:

• К СИА.

№ 79

Назначение сигнала “КВУ”:

• Разделение областей памяти ОЗУ и ВУ.

№ 80

Процессор перед вводом данных располагает сведениями:

• Адресом обращения в RA и адресом приемника этих данных (RGK или RA или RD1 или RD2).

№ 81

Состояние линий BUS4 (15-13) при загрузке канала адресом 2000 восьмеричное:

• 0.0.0.

№ 82

Чтение данных канала обеспечивается средствами:

• KAD, F(Y21), DA, Y6, BUS3, Y18.

№ 83

Загрузка адреса или чтение данных канала организована:

• Y21(0,1).

№ 84

Системный сигнал подтверждает, что адрес обращения в канале:

• КСИА, Y16, Y21.

№ 85,86

- подтверждает, что данные ВУ переданы и является запросом данных от ВУ:

• КСИА, КСИП, КВВОД.

№ 87

R7 после выполнения текущей команды должен иметь:

• Модифицированное содержимое, плюс 2.

№ 88

Данные, принятые RGK, поступают:

• В центральное устройство управления.

№ 89

Логическая 1 в линиях шины BUS4 представлена:

• Низким уровнем электропитания РАЛУ.

№ 90

Логическая 1 на входе А шинного формирователя F представлена:

• Высоким уровнем электропитания РАЛУ.

№ 91

Последовательность, интерпретирующая команду: MOV#D, @#A, включает:

• 9 микропрограммных секций.

№ 92

Для обращения к ВУ за записью данных необходимы рабочие регистры:

• RA, RD1.

№ 93

Запись данных в канал (линии KAD) организуется:

• Y21 = 0, Y13.

№ 94

Различие обращения к ОЗУ и ВУ:

• КВY (0 или 1).

№ 95

В машинном коде представления команды имеют поля адреса источника и приемника данных:

• Шесть двоичных или два 2-8-ричных.

№ 96

Для интерпретации косвенного метода адресации источника данных требуется:

• Две микропрограммные секции: 10 и 7.

№ 97

- косвенно-автодекрементного метода:

• Четыре: 9, 10, 6 и 7.

№ 98

В методах адресации данных используются операции:

• Пересылка, сложение, вычитание.

№ 99

Предварительно уменьшения содержимого регистров общего назначения требуют:

• Косвенно-автодекрементный, автодекрементный методы адресации данных.

№ 100

Причина цепочек различной длины (количество слов), в представлении команды на уровне машинных кодов:

• В указании методами адресации адреса источника и/или приемника данных.

№ 101

В канал (линии KAD) может быть загружено содержимое рабочих регистров процессора:

• RA или RD1.

№ 102

Процедура вычисления адреса ветвления выполняется,

• когда код операции управления программой совпадает с признаками результата предыдущей команды программы.

№ 103

Если условие ветвления не выполнено, процессор будет выполнять команду:

• с адресом, указанным в R7.

№ 104

Ветвление программы осуществляется:

• Относительно содержимого R7.

№ 105

Последовательность, интерпретирующая команду MOV R1, R2 управляющей микроЭВМ, включает:

• 4 микропрограммные секции.

№ 106

- ADD R1, R2:

• 4.

№ 107

- SUB R1, R2:

• 4.

№ 108

- MOV (R1), R2:

• 6.

№ 109

- MOV (R1), +(R2):

• 8.

№ 110

- MOV -(R1), (R2):

• 8.

| на главную | база по специальностям | база по дисциплинам | статьи |

Другие статьи по теме